rejunity/z80-open-silicon

Fork: 25 Star: 613 (更新于 2024-11-18 00:24:58)

license: Apache-2.0

Language: Verilog .

Z80 open-source silicon clone. Goal is to become a silicon proven, pin compatible, open-source replacement for classic Z80.

Announcement

On April 15 of 2024 Zilog has announced End-of-Life for Z80, one of the most famous 8-bit CPUs of all time.

It is a time for open-source and hardware preservation community to step in with a Free and Open Source Silicon (FOSS) replacement for Zilog Z80.

GOAL: To develop a drop-in Z80 replacement in 8-bit home computers such as ZX Spectrum and recent DIY computer kits such as RC2014.

The first fabrication of FOSS clone of Z80 is scheduled for June of 2024!

Modern free and open source silicon clone of Zilog's Z80

On the path to become a silicon proven, pin compatible, open-source replacement for classic Zilog Z80.

FOSS Z80 leverages OpenROAD flow and FOSS 130 nm Skywater PDK to synthesize production ready silicon. Tiny Tapeout infrastructure is used to test and pool design with many others to reduce the cost of physical chip fabrication at Skywater Foundries.

The first iteration of FOSS Z80 silicon

The first iteration is developed with Tiny Tapeout 07 using 130 nm process and fits on a 0.064 mm2 die area. The first fabrication is scheduled for June of 2024 as a part of CI 2406 Shuttle.

Check status here: https://app.tinytapeout.com/projects/668

![]()

The implementation is based around Guy Hutchison's TV80 Verilog core.

Below is the image of GDSII integrated circuit layout for FOSS Z80. It is the result of automatic place-and-route flow in OpenROAD using 130 nm "gates" logic elements.

![]()

Plan

- Submit with Tiny Tapeout 07

- Write basic documentation for Tiny Tapeout 07: docs/info.md

- Tapeout with ChipIgnite in QFN64 package, create a PCB adapter from QFN64 to DIP40

- Add thorough tests for all Z80 instructions including the 'illegal' ones ZEXALL to a testbench

- Add thorough timing test of the input/output signals

- Integrate the netlist based Z80 core into the testbench for ultimate validation

- Compare different implementations: Verilog core A-Z80, Netlist based Z80Explorer, etc

- Create gate-level layouts that would resemble the original Z80 layout, see the original chip dies below. Zilog designed Z80 by manually placing each transistor by - - [ ] Tapeout with DIP40 package hand.

How to Contribute

Join the Tiny Tapeout Discord forum.

Browse issues.

Quick start

For project overview, take a look at the slide deck and video where we discuss FOSS Z80 project with Matthew Venn.

Code:

- You can find the top module in src/tt_um_rejunity_z80.v. It instantiates Z80 and adheres to TinyTapeout constraints including multiplexing the output pins onto the 8 pins of TinyTapeout chip.

- The core Verilog Z80 implementation is in src/tv80 folder.

- The configuration for OpenROAD synthesis and place-and-route flow is in the src/config.tcl file.

- Finally, the testbench is implemented in src/test/test.py.

Generated layout artifacts are in gds folder. You can use KLayout viewer to inspect them:

Run it locally

Follow the instructions from Tiny Tapeout's Testing Your Design Guide and install required packages.

sudo apt install iverilog verilator

pip3 install cocotb pytest

Next, run the testbench.

cd src

make

If you are succesfull, you should see the tests passing:

Machines using Z80

These machines are considerd as test-cases for hardware Z80 replacement:

- ZX Spectrum 16K - ?

- ZX Spectrum 48K - (interrupted) 3.5 MHz Z80 <= ULA <= 14MHz crystal

- ZX Spectrum 128K - (interrupted) 3.54690 MHz Z80 <= ULA <= 17.7345 crystal (see analogue part of the schematics)

- Amstrad CPC - 4 MHz Z80 <= GA4007 <= 16Mhz crystal

- MSX1 - 3.579 MHz <= ??? TMS9918/9928/9929 <= ???

- MSX2 - 3.579 MHz <= V9938 <= 21.328125

- MSX2 - 3.579 MHz <= S3527 <= V9938 <= 21.328125

- SG-1000 CPU sheet VDP sheet - 3.58 MHz Z80 <= TMS9918ANL (NTSC) <= 10.73863 MHz crystal

- Sega Master System - 3.58 MHz Z80 <= VDP 315-5124 <= 10.738 MHz

- ColecoVision console - 3.57954 MHz Z80 <= /2 <= 7.15909 MHz crystal

- TSR80 CPU sheet clock sheet - 1.774 MHz Z80 <= /6 <= 10.6445 MHz

- Sinclair ZX80, ZX81 - 3.25 MHz Z80 (NEC μPD780C-1)

Recent DYI computer kits are also perfect test-cases for Z80 FOSS:

- RC2014 modular computer - 8K ROM, 32K RAM, runs at 7.3728 MHz

- Zeal 8-bit Computer - 32K ROM, from 128KB up 512KB of RAM, runs at 10 MHz

- LiNC80 microcomputer kit - 16K/64K ROM, 64K RAM, runs at 7.3728 MHz

Z80

Pinout

,-------.___.-------.

<-- A11 |1 40| A10 -->

<-- A12 |2 39| A9 -->

<-- A13 |3 Z80 CPU 38| A8 -->

<-- A14 |4 37| A7 -->

<-- A15 |5 36| A6 -->

--> CLK |6 35| A5 -->

<-> D4 |7 34| A4 -->

<-> D3 |8 33| A3 -->

<-> D5 |9 32| A2 -->

<-> D6 |10 31| A1 -->

VCC |11 30| A0 -->

<-> D2 |12 29| GND

<-> D7 |13 28| /RFSH -->

<-> D0 |14 27| /M1 -->

<-> D1 |15 26| /RESET <--

--> /INT |16 25| /BUSRQ <--

--> /NMI |17 24| /WAIT <--

<-- /HALT |18 23| /BUSAK -->

<-- /MREQ |19 22| /WR -->

<-- /IORQ |20 21| /RD -->

`-------------------'

Documentation

- Z80 Datasheet

- Zilog Users Manual and Mostek's Users Manual

- Zilog Data Book

- All the information about Z80

- Undocumented instructions

- Opcode table and timing

Oral History of the Development of the Z80

Oral History Panel on the Founding of the Company and the Development of the Z80 Microprocessor

M. Shima on Demystifying Microprocessor Design

Z80 Patents

- (expired) Patent US4605980 -- input voltage spike protection

- (expired) Patent US4332008A -- ???

- (expired) Patent US4486827A -- reset circuitry

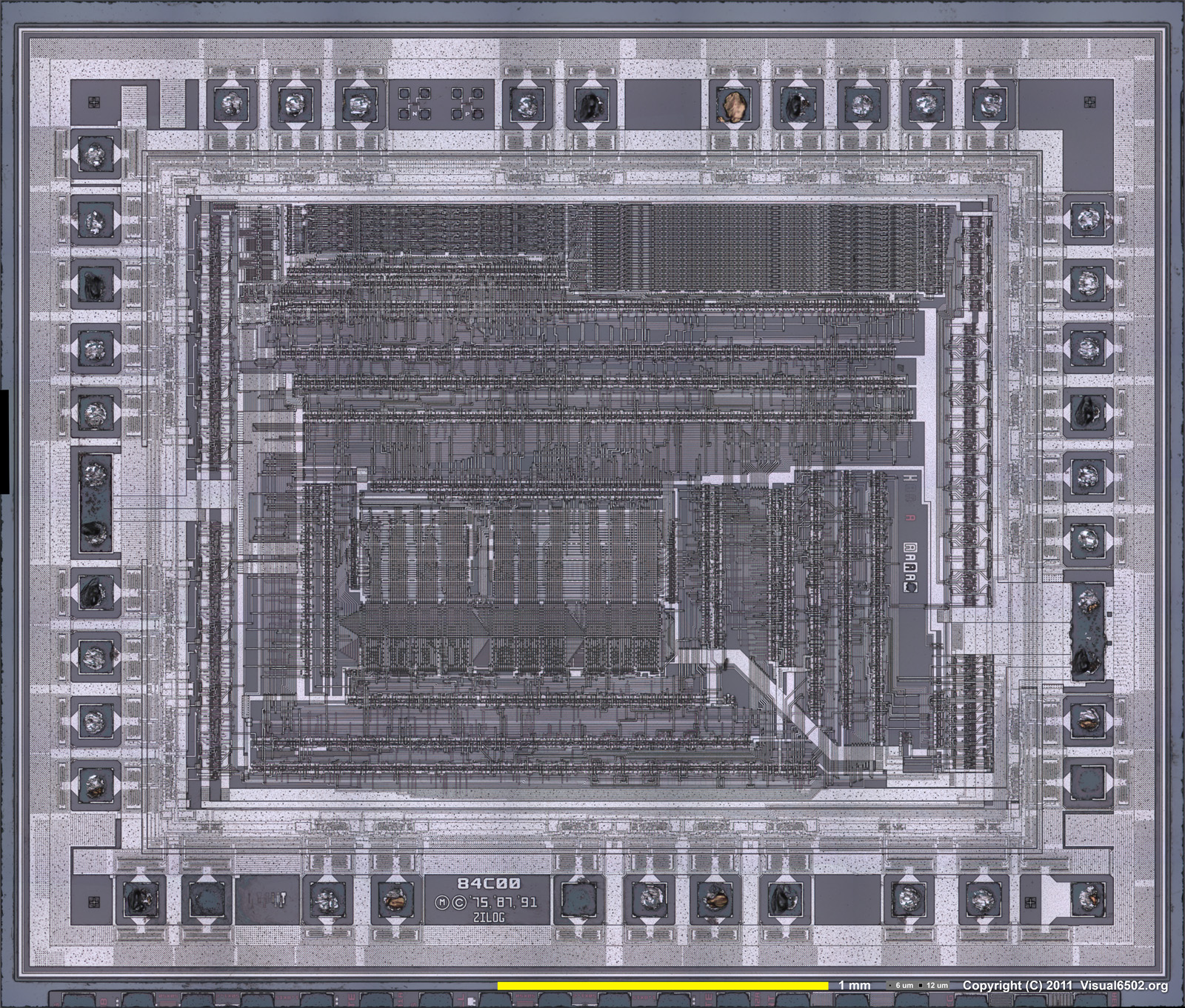

Z80 Die shots

- How to "read" die shots

- nMOS variants Z8400 with 'Zilog 75' marking and Zilog Z8400 with 'DC' letter marking

- CMOS variants Zilog Z84C00 and its 8MHz version

- Nintendo Z80 variant from Super Game Boy SGB-CPU 01 produced in 1994

- Sean Riddle's image of the official second-source Mostek MK3880 metal layer removed

- Pauli Rautakorpi's images of Z80 clones: National Semiconductor NSC800, Mostek MK3880, MME9201 with 'U880/5' markings

- Zeptobar’s images of Zilog Z0840004PSC from 1990, Soviet CMOS KR1858VM3 with an uncommon layout, MME Z80A a clone on a large 5um process, Soviet KR1858VM1 a clone of U880/6 which in turn was an unlicensed clone of Z80, Soviet T34VM1 based on U880/5

- nMOS variant GoldStar Z80 can be found in "Finding traps" article by Sergei Skorobogatov

Z80 Reverse Engineering

- Finding "traps" in Zilog Z80 CPU by Sergei Skorobogatov

- Comparing Z80 to 6502 and ARM1

- Z80 Instruction Register deciphered

- Z80 Tri-stated Data & Address bus gates

- Z80 (un)documented behavior

- The instruction decode PLA in the Z80 microprocessor

- Why the Z-80's data pins are scrambled

- How the Z80's registers are implemented

- The Z-80's 16-bit increment/decrement circuit reverse engineered

- The Z-80 has a 4-bit ALU

- XOR, the silicon for two interesting gates explained

- WZ aka MEMPTR, esoteric register of the Z80

- Undocumented flags part of Z80 Decoder logic analyser / bus capture

Existing Z80 implementations

- TV80 in Verilog https://github.com/hutch31/tv80

- TV80 in Verilog https://github.com/Obijuan/Z80-FPGA

- A-Z80 in Verilog https://github.com/gdevic/A-Z80 its overview and details

- Z80 net-list level emulator https://github.com/gdevic/Z80Explorer and its overview and Users Guide

- Online Z80 net-list emulator at Visual6502.org

What is Tiny Tapeout?

Tiny Tapeout is an educational project that aims to make it easier and cheaper than ever to get your digital designs manufactured on a real chip.

To learn more and get started, visit https://tinytapeout.com.

Resources

最近版本更新:(数据更新于 2024-10-28 15:01:28)

主题(topics):

chip, cpu, foss, retrocomputing, tapeout, tinytapeout, verilog, z80

rejunity/z80-open-silicon同语言 Verilog最近更新仓库

2020-07-07 05:38:58 The-OpenROAD-Project/OpenROAD

1970-01-01 00:00:00 SI-RISCV/e200_opensource

1970-01-01 00:00:00 fyquah/FPGA-passive-autofocus

1970-01-01 00:00:00 XUANTIE-RV/openc910

1970-01-01 00:00:00 matt-kimball/toygpu

1970-01-01 00:00:00 davidthings/tinyfpga_bx_usbserial